Specifikation

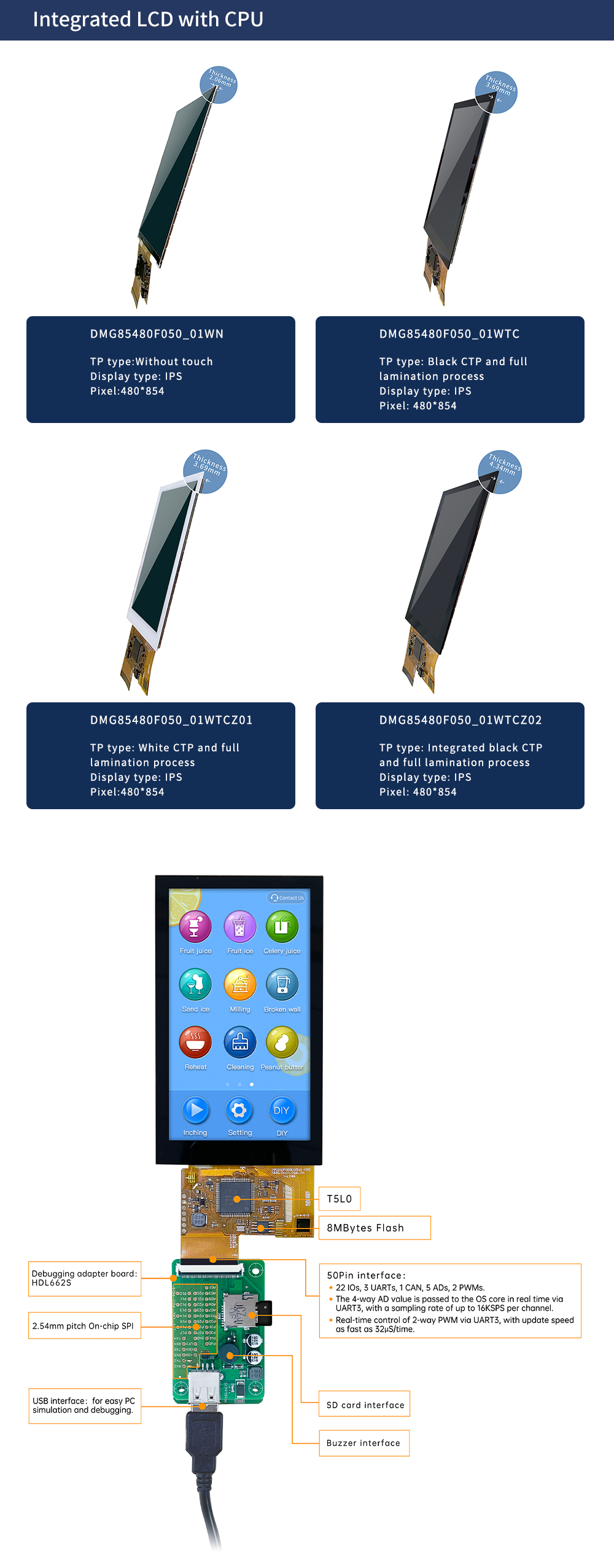

| T5L0 ASIC | T5L0 ASIC är en lågeffekts, kostnadseffektiv, GUI och applikations högintegrerad enkelchips dubbelkärnig ASIC designad av DWIN Technology för små LCD-skärmar och massproducerade 2020. | ||

| Färg | 262K färger | ||

| LCD-typ | IPS-TFT-LCD, | ||

| Betraktningsvinkel | Bred synvinkel, typiskt värde på 85°/85°/85°/85°(L/R/U/D) | ||

| Upplösning | 480×854 | ||

| Bakgrundsbelysning | LED | ||

| Ljusstyrka | DMG85480F050_01WN:400nit DMG85480F050_01WTC:350nit DMG85480F050_01WTCZ01:350nit DMG85480F050_01WTCZ02:100nit | ||

| Typ | CTP (Kapacitiv pekskärm) | ||

| Strukturera | G+G-struktur | ||

| Pekläge | Stöd peka och dra | ||

| Ythårdhet | 6H | ||

| Ljustransmittans | över 90 % | ||

| Liv | Över 1 000 000 gånger beröring | ||

| Strömspänning | 3,6~5,5V, typiskt värde på 5V | ||

| Operation Aktuell | VCC=5V, max bakgrundsbelysning, 300mA | ||

| VCC=5V, bakgrundsbelysning av, 95mA | |||

| Arbetstemperatur | -10℃~60℃ | ||

| Förvaringstemperatur | -20℃~70℃ | ||

| Arbetsfuktighet | 10%~90%RH, typiskt värde på 60%RH | ||

| Användargränssnitt | 50 Pin_0,5 mm FPC | ||

| Baudrate | 3150~3225600 bps | ||

| Utspänning | Utgång 1;3,0~3,3 V | ||

| Utgång 0;0~0,3 V | |||

| Inspänning (RXD) | Ingång 1;3,3V | ||

| Ingång 0;0~0,5V | |||

| Gränssnitt | UART2: TTL; UART4: TTL;( Endast tillgänglig efter OS-konfiguration) UART5: TTL; (Endast tillgängligt efter OS-konfiguration | ||

| Dataformat | UART2: N81; UART4: N81/E81/O81/N82;4 lägen (OS-konfiguration) UART5: N81/E81/O81/N82;4 lägen (OS-konfiguration) | ||

| Stift | Definition | I/O | Funktionsbeskrivning |

| 1 | 5V | I | Strömförsörjning, DC3,6-5,5V |

| 2 | 5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I | 5 ingångs ADC.12-bitars upplösning vid 3,3V strömförsörjning.0-3,3V ingångsspänning.Förutom AD6 skickas resten av data till OS-kärnan via UART3 i realtid med 16KHz samplingsfrekvens.AD1 och AD5 kan användas parallellt, och AD3 och AD7 kan användas parallellt, vilket är lika med två 32KHz samplings AD.AD1, AD3, AD5, AD7 kan användas parallellt, vilket är lika med en 64KHz samplings AD;data summeras 1024 gånger och divideras sedan med 64 för att erhålla ett 64Hz 16bit AD-värde genom översampling. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +3,3 | O | 3,3V utgång, maximal belastning på 150mA. |

| 12 | SPK | O | Extern MOSFET för att driva summer eller högtalare.Det externa 10K-motståndet ska dras ner till marken för att säkerställa att strömmen är på låg nivå. |

| 13 | SD_CD | I/O | SD/SDHC-gränssnitt, SD_CK ansluter en 22pF-kondensator till GND nära SD-kortgränssnittet. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | I/O | |

| 16 | SD_D2 | I/O | |

| 17 | SD_D1 | I/O | |

| 18 | SD_D0 | I/O | |

| 19 | PWM0 | O | 2 16-bitars PWM-utgång.Det externa 10K-motståndet ska dras ner till marken för att säkerställa att strömmen är på låg nivå.OS-kärnan kan styras i realtid via UART3 |

| 20 | PWM1 | O | |

| 21 | P3.3 | I/O | Om du använder RX8130 eller SD2058 I2C RTC för att ansluta till båda IO:erna, ska SCL anslutas till P3.2 och SDA kopplas till P3.3 parallellt med 10K resistor pull-up till 3,3V. |

| 22 | P3.2 | I/O | |

| 23 | P3.1/EX1 | I/O | Den kan användas som en extern avbrott 1-ingång samtidigt och stöder både lågspänningsnivå eller bakkantsavbrottslägen. |

| 24 | P3.0/EX0 | I/O | Den kan användas som en extern avbrott 0-ingång samtidigt och stöder både lågspänningsnivå eller bakkantsavbrottslägen. |

| 25 | P2.7 | I/O | IO-gränssnitt |

| 26 | P2.6 | I/O | IO-gränssnitt |

| 27 | P2.5 | I/O | IO-gränssnitt |

| 28 | P2.4 | I/O | IO-gränssnitt |

| 29 | P2.3 | I/O | IO-gränssnitt |

| 30 | P2.2 | I/O | IO-gränssnitt |

| 31 | P2.1 | I/O | IO-gränssnitt |

| 32 | P2.0 | I/O | IO-gränssnitt |

| 33 | P1.7 | I/O | IO-gränssnitt |

| 34 | P1.6 | I/O | IO-gränssnitt |

| 35 | P1.5 | I/O | IO-gränssnitt |

| 36 | P1.4 | I/O | IO-gränssnitt |

| 37 | P1.3 | I/O | IO-gränssnitt |

| 38 | P1.2 | I/O | IO-gränssnitt |

| 39 | P1.1 | I/O | IO-gränssnitt |

| 40 | P1.0 | I/O | IO-gränssnitt |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0,0 | I/O | IO-gränssnitt |

| 46 | P0.1 | I/O | IO-gränssnitt |

| 47 | CAN_TX | O | CAN-gränssnitt |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (UART2 seriell port för OS-kärna) |

| 50 | UART2_RXD | I |